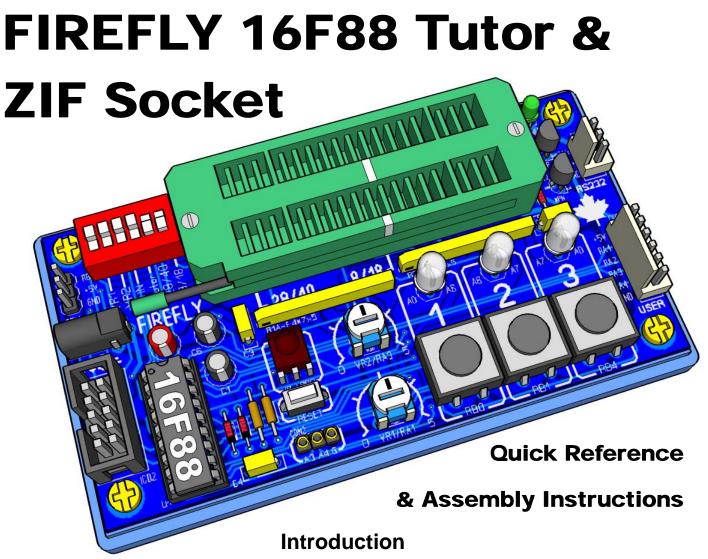

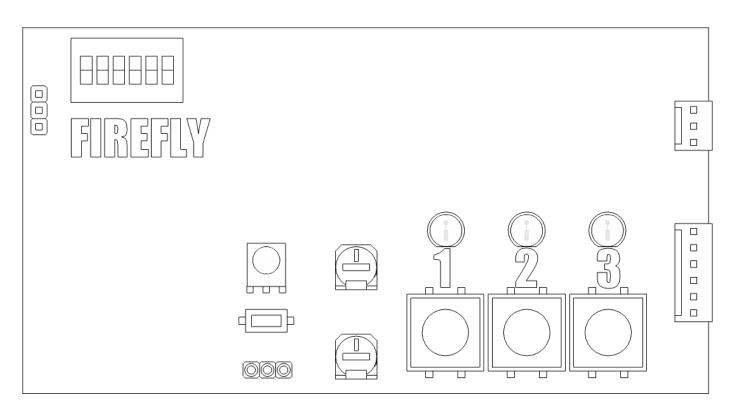

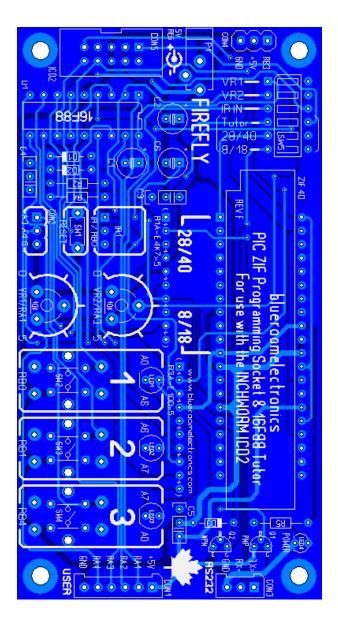

It's surprising how many people wanted to get into microcontroller programming but have no idea what to do for their first project let alone how to even program one. Secondly even though ICP is available there is still a demand for ZIF (Zero Insertion Force) programming sockets. So I combined two kits into one. Firefly can be built as a 16F88 trainer, a PIC ZIF programming socket or both. The Firefly was designed as a PIC tutor companion kit to the Inchworm ICD2.

#### 16F88 tutor highlights

- Microchip PIC16F88 with programmable internal 8 speed oscillator, 31.25 KHz to 8MHz

- 3 dual color Red / Green LEDs & 3 User Pushbuttons (two sizes available economy / large)

- 38KHz Infrared sensor & 2 Switch Selectable Variable Resistors for 0-5V on RA1 / RA3

- RS232 connector with inverting transistors (requires optional DE9 to 3pin cable adapter)

- 6 pin User I/O port for external expansion and your own projects

- 3 pin servo style connector for Servos, IR LED, Buzzer, Piezo speakers, switches etc.

- 3 hole iButton® / 1-wire and quick test socket, small 57mm x 107mm PCB

- ZIF socket for programming 8/14/18/20\*/28/40 pin Flash PICs

- Mode switch, Reset switch, 1.3mm 5VDC power jack & Inchworm ICD2 connector

\*although not on the silk-screening 20pin devices can be programmed using the 8/18 setting

### Why the PIC16F88...

The PIC16F88 is the current king of the 18pin 16F series PICs. This inexpensive and very powerful micro is just packed with internal peripherals. Although there are literally hundreds of PICs to choose from the 16F88 stood on top of the pack for one reason more than any other; **the 16F88 has the hardware debugger built in.** Whether you're new with PICs or old school, when you're working with any microcontroller there will be a time when you wish you could see what that little black box was thinking on the inside. Well that's what a debugger lets you do; you can set breakpoints *stop a running program* and see exactly what the processor sees. You can even modify the data. Difficult to find program errors can be spotted and wiped out with relative

|               | 16F84A | 16F628A | 16F88     |  |

|---------------|--------|---------|-----------|--|

| Flash         | 1024   | 2048    | 4096      |  |

| RAM           | 68     | 224     | 368       |  |

| EEPROM        | 64     | 128     | 256       |  |

| Internal Osc  | No     | 2 speed | 8 speed   |  |

| A/D           | None   | None    | 7 @ 10bit |  |

| Timers        | 1      | 3       | 3         |  |

| USART         | No     | Yes     | Yes       |  |

| PWM / CCP     | No     | 1       | 1         |  |

| Comparators   | No     | 2       | 2         |  |

| Self Flashing | No     | No      | Yes       |  |

| Debugger      | No     | No      | Yes       |  |

ease and as a learning tool the mysteries of the internal workings are quickly revealed.

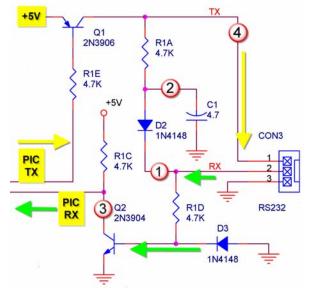

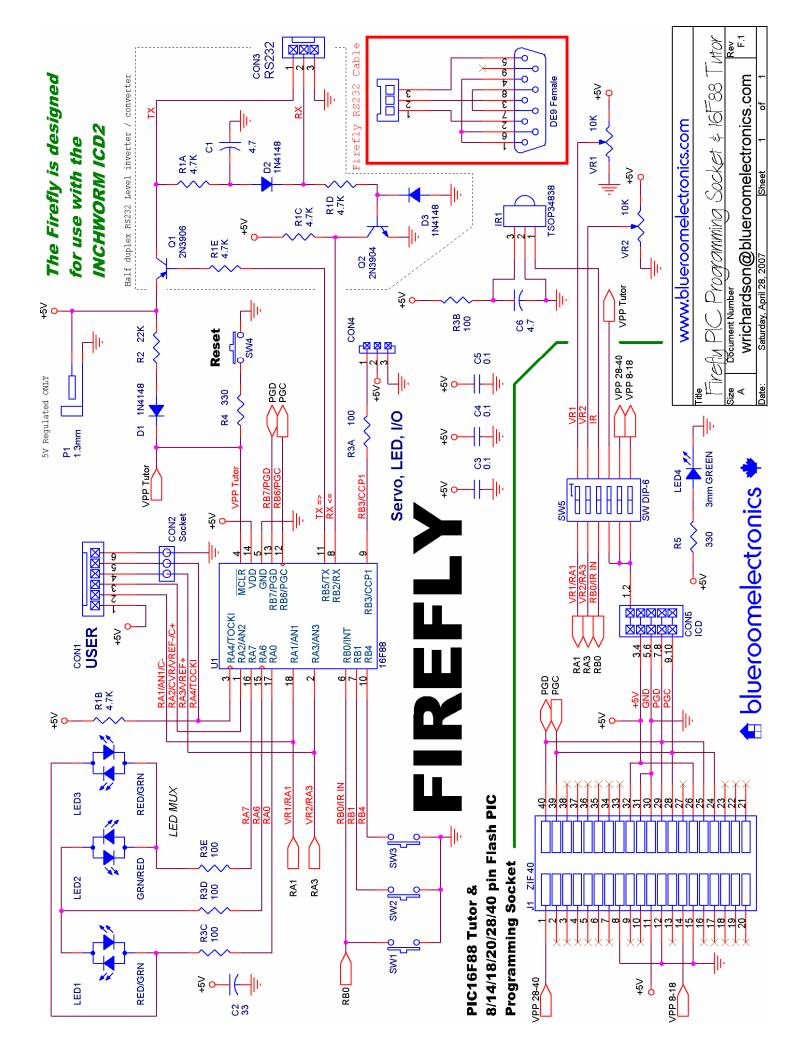

#### **Circuit Description**

A detailed description of Firefly built in peripherals can be found in the "Firefly User Guide" Although Firefly is a fairly straight forward design; one feature worth further examination would be the RS232 level shifter. When using the hardware USART the data on the RX & TX pins has to be inverted and level shifted to be useful as RS232. This type of RS232 inverter requires the hosts idle "*Mark*" TX voltage is at or below GND (*ideally lower than -3V*).

- 1. D2 borrows power from the target RS232 TX pin.

- 2. C1 charges to a negative voltage when RX is idling and R1A pulls TX to this negative (idle / mark) voltage.

- 3. Inverted by Q2 (RX incoming RB2) from target RS232.

- 4. Inverted by Q1 (TX outgoing RB5) from U1-16F88.

\*If your target serial port does not pull RX to a negative voltage when idle; the serial port may not operate because the TX line will never pull to a MARK (negative) voltage. Test the voltage at point ①

Other noteworthy features would be the multiplexed (Mux) LED display. The Red / Green two lead LEDs can only be turned on one at a time. This scheme; sometimes called Charlieplexing allows very few I/O pins to run many LEDs. With the Firefly we can effectively control six LEDs with three pins, to make more than one LED appear lit at a time; but to do this we have to continuously refresh the display faster than 40Hz. This is not difficult to program, as an example try removing all the "call Delay" lines in Blinky 16F88 on page 9 and the result will be the LEDs will appear Orange (*they're actually only lit one at a time, try single stepping in debug mode and you'll see*).

The IR1 decoder TSOP34838 has an internal 38KHz band pass filter so it will only see IR transmissions that are modulated at or near 38KHz; this is designed to prevent ambient light from falsely triggering the sensor. IR1 also shares RB0 with Pushbutton SW2. Therefore when you're using SW2 *Pushbutton 1* you should disable IR1 using SW5-3 is the reverse is true when using IR1 is SW2)

#### **Necessary Tools** (not included in kit)

As with any electronic kit the following tools are essential:

- Low wattage fine tip soldering iron <50W

- Resin core solder

- Wire cutters or side cutters (small)

- Needle nose pliers (small)

- Slotted screwdriver (small)

- Phillips screwdriver (small)

- Multimeter (this really is a must for any electronics project)

#### Assembly

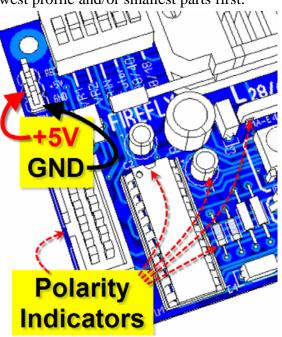

Traditionally it's easiest to assemble a circuit board with the lowest profile and/or smallest parts first.

Install 5% resistors R2, R4, R5 Small signal diodes D1 thru D3 (Red 1N4148) Note: diodes use a colored band to denote polarity SIP resistors Isolated type R1 (4.7K), R3 (100ohm) (You can use 1/8W resistors if you don't have the SIPs) IC socket for U1 (notice notch orientation) Transistors Q1 (2N3906) / Q2 (2N3904) Power LED4 (green) LED1, LED2, LED3 (Dual Color RED / GREEN) *Note: LEDs have a flat side indicating polarity* Capacitors C3, C4, C5 (note lead spacing) Capacitors C1, C6 (4.7uF) Capacitor (note polarity) C2 (33uF) Switches SW1, SW5 (note pin 1 on SW5) Switches SW2, SW3, SW4 (one of two sizes will fit) 38KHz IR decoder IR1 (see the cover diagram for details) Optional 1.3mm coax power jack P1 regulated 5V required Connectors CON1 thru CON5 (Use the Firefly cover illustration as a guide)

Optional install Aries ZIF socket. (*The 3M Textool ZIF will not fit and is not recommended*) Note: The Aries ZIF socket and SW5 can be a very tight fit. It's advised to place them both on the board before soldering either.

#### **Initial Testing**

Before installing IC1 (PIC16F88) apply power to the board, this is best done by attaching an ICD2 such as the Inchworm to the ICD2 connector (CON5). The 3mm green power LED4 should be on. *Note: The* #2 LED may be on (Green) when the 16F88 is blank. This is normal as the comparators (which by defalt are on) are driving the pins.

## **Final Assembly**

Make sure the board is un-powered then install U1 (PIC16F88). If you've built a Tutor try out the program "Blinky VR1" near the end of this document for testing the BiColor LEDs and VR1. There will be Firefly and other PIC related projects added to the <u>blueroomelectronics</u> site regularly. See the project link on the site for details.

Make sure to download the 16F88 datasheet from Microchip for a detailed explanation of the 16F88.

### Parts List FIREFLY T (Tutor)

#### Capacitors

| 1 | C1     | 4.7uF 16V (subminiature)                              |

|---|--------|-------------------------------------------------------|

| 1 | C2     | 33uF 6.3V (subminiature 22uf thru 47uf may be used)   |

| 3 | C3,4,5 | 0.1uF                                                 |

| 1 | C6     | 4.7uF 6.3V (subminiature 4.7uf thru 47uf may be used) |

#### Resistors ¼W (tan body, 4 color bands)

| 1 | R2       | 22K      | Red, Red, Orange, Gold            |

|---|----------|----------|-----------------------------------|

| 2 | R4, 5    | 330      | Orange, Orange, Brown, Gold       |

| 1 | R1       | 4.7K x 5 | SIP 10pin 5 independent resistors |

| 1 | R3       | 100 x 5  | SIP 10pin 5 independent resistors |

| 2 | VR1, VR2 | 10K      | 10K Trimmer potentiometers        |

#### **Semiconductors**

| 3<br>3<br>1 | D1, 2, 3<br>LED1, 2, 3<br>LED4 | 1N4148 Small Signal Diode<br>3mm or 5mm RED/GREEN dual color LED (LT<br>3mm GREEN LED | 29 | 3SJW | 2 L | ead) |                |   |   |

|-------------|--------------------------------|---------------------------------------------------------------------------------------|----|------|-----|------|----------------|---|---|

| 1           | IR1                            | TSOP34838 38KHz IR detector                                                           | _  |      |     |      |                |   |   |

| 1           | Q1                             | 2N3906 PNP (EBC)                                                                      |    |      |     |      |                |   |   |

| 1           | Q2                             | 2N3904 NPN (EBC)                                                                      |    | ۲۳   | ۲   | Μ    | ۲ <sup>w</sup> | ۲ | 1 |

| 1           | U1                             | PIC16F88                                                                              |    |      |     |      |                |   |   |

#### Switches

| 1 | SW1     | Small pushbutton (450-1173-ND)                   |

|---|---------|--------------------------------------------------|

| 3 | SW2,3,4 | Pushbutton (Small or Large 450–1131–ND see text) |

| 1 | SW5     | DIP Switch 6 position                            |

#### **Connectors**

| 1 | CON 1 | 6pin Molex connector | +5V, RA1, RA2, RA3, RA4, GND |

|---|-------|----------------------|------------------------------|

| 1 | CON2  | 3pin machine socket  | RA3, RA4, GND                |

| 1 | CON3  | 3pin Molex connector | TX, RX, GND                  |

| 1 | CON4  | 3pin header          | RB3, +5V, GND                |

| 1 | CON5  | ICD 2x5 PCB Male     | ICD2 (Inchworm)              |

#### Miscellaneous

| 1 | 18-pin | IC Socket                         |

|---|--------|-----------------------------------|

| 1 | P1     | 1.3mm PCB RA Coax Jack (optional) |

#### **Optional Accessories**

| 1 | Enclosure        | Hammond 1591B (112mm x 62mm) or 1591BC clear lid |

|---|------------------|--------------------------------------------------|

| 1 | 5VDC Adapter     | 5VDC 1.3mm center positive coax AC adapter       |

| 1 | 3pin RS232 Cable | See text for building instructions               |

## Parts required for Firefly Z (ZIF) option\*

1 J1

Aries 40-6554-10 (*3M / Textool may require modification*)

\*To build a "Firefly Z" ZIF only option only J1, SW5, CON5 & C3 are required. LED4 and R5 are optional but recommended.

## Parts required for Firefly TZ (Tutor & ZIF)

The Firefly TZ requires all parts listed above

Part numbers ending in .ND can be found at <u>http://www.Digikey.com</u>

w

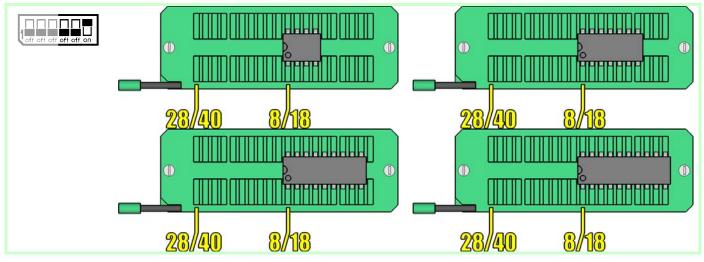

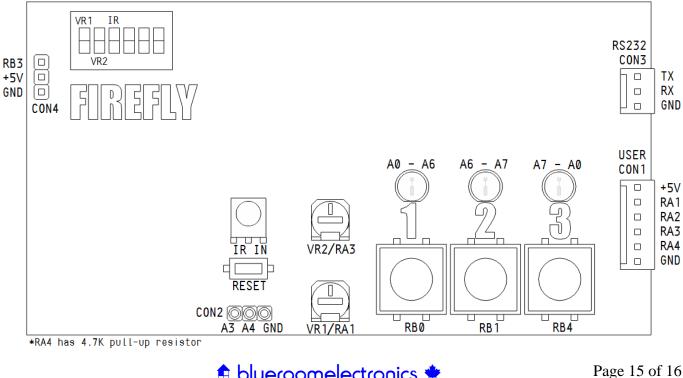

In the upper left corner of the Firefly there is a six position DIP switch (shown in Tutor default mode)

| Functions fro | Functions from 1-6 (left to right) $enable = on / up \& disable = off / down$ |                                                                            |  |  |  |

|---------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|

| SW5-1         | VR1                                                                           | (0-5V pot) = up, USER port RA1 I/O = down                                  |  |  |  |

| SW5-2         | VR2                                                                           | (0-5V pot) = up, USER port RA3 I/O = down                                  |  |  |  |

| SW5-3         | IR IN                                                                         | (38 KHz IR) receiver on RB0 = up, Pushbutton 1 is always enabled           |  |  |  |

| SW5-4         | Tutor                                                                         | (ICD2 controls U1, 16F88), down allows 16F88 free running mode & SW1 RESET |  |  |  |

| SW5-5         | 28/40                                                                         | (ICD2 setting for programming 28 or 40 pin 5v tolerant PICs)               |  |  |  |

| SW5-6         | 8/18                                                                          | (ICD2 setting for programming 8, 14, 18 or 20 pin 5v tolerant PICs)        |  |  |  |

Reset switch SW1 will function when SW5-4 is down (off). Normally when you're working with an ICD2 you control reset via MPLAB.

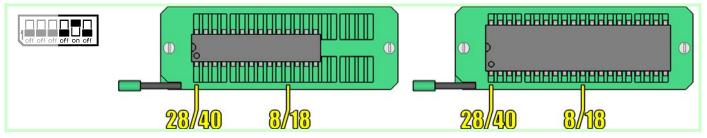

### Firefly RS232 Cable (DTE)

The illustration on the right should help you to build your Firefly to DE9 RS232 cable. This type of cable can connect directly to your PCs serial port or other DCE *Data Computer Equipment* terminals or devices.

| Firefly    |       | 1 | 2 |       | 3 |       |     |     |   |

|------------|-------|---|---|-------|---|-------|-----|-----|---|

| DE9 Female | 1,4,6 | 2 | 3 | 1,4,6 | 5 | 1,4,6 | 7,8 | 7,8 | 9 |

The white wires in the close-up are for loopback connections. Use shielded cable for lengths over 1' or 30cm (*Solder the shield conductor to the DE9 connector*) Note: the colors shown are for reference only. Your cables colors may be different.

It's a good idea to use a DE9 shell on the cable.

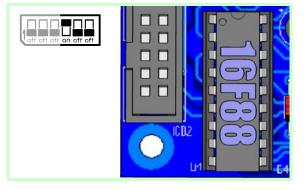

#### **ZIF (Zero Insertion Force) Programming Socket**

The ZIF socket option when combined with an Inchworm ICD2 is compatible with the following PICs. PICs with 20pins or less are inserted into the socket at pin#11, it's recommended to mark this pin location on the socket with a silver sharpie marker or a small dash of paint (see the cover drawing for suggestions)

#### ZIF Socket Compatible PICs with 0.6" & 0.3" wide DIP

12F508, 12F509, 12F510, 12F629, 12F635, 12F675, 12F683

16Fxxxx series : 505, 506, 54, 616, 627x, 628x, 630, 631, 636, 648A, 676, 677, 684, 685, 687, 688, 689, 690, 716, 72, 73, 737, 74, 747, 76, 16F767, 16F77, 16F777, 16F785, 16F818, 819, 83, 84A, 87, 870, 871, 872, 873x, 16F874x, 876x, 877x, 88, 883, 884, 886, 887, 913, 914, 916, 917, HV616 18Cxxxx series : 242, 252, 442, 452

18Fxxxx series : 1220, 1230, 1320, 1330, 2220, 2221, 2320, 2321, 2331, 2410, 242, 2420, 2431, 2439, 2450, 2455, 248, 2480, 2510, 2515, 252, 2520, 2525, 2539, 2550, 258, 2580, 2585, 2610, 2620, 680, 2682, 2685, 4220, 4221, 4320, 4321, 4331, 4410, 442, 4420, 4431, 4439, 4450, 4455, 448, 4480, 4510, 4515, 452, 4520, 4525, 4539, 4550, 458, 4580, 4585, 4610, 4620, 4680, 4682, 4685

# The Programming Switches (VPP select) and the ZIF socket

Programming 8/14/18/20 DIP PICs (Tutor off, 28/40 off, 8/18 on)

### Programming 28/40 pin PICs (Tutor off, 28/40 on, 8/18 off)

Programming the Tutor 16F88 (Tutor off, 28/40 on, 8/18 off)

|       | _   |     | _   | _   |     |

|-------|-----|-----|-----|-----|-----|

|       |     |     |     |     |     |

|       |     |     |     |     |     |

| 1 off | off | off | off | off | off |

| 011   | 011 | 011 | 011 | 011 | 011 |

Free Running the Tutor 16F88

| ;*** sleep16F88.asm<br>LIST p=16F88             |

|-------------------------------------------------|

| INCLUDE "p16f88.inc"<br>CONFIG _CONFIG1, 0x3F7C |

| banksel TRISA                                   |

| movlw b'00111111'                               |

| movwf TRISA                                     |

| banksel PORTA                                   |

| movlw 0x80                                      |

| movwf PORTA ;LED2 red                           |

| clrwdt                                          |

| goto \$-1                                       |

| END                                             |

#### and Tutor / ZIF Interference

Depending on the program running on 16F88 (Tutor); it's possible to interfere with the ZIF socket. The program "sleep16F88.asm" should correct the problem when using the ZIF socket. If this fails you can hold down the reset button while using the ZIF socket or remove the 16F88.

> blueroomelectronics \* Smart Kits build Smart People

Page 7 of 16 revised 9/4/2007

## **16F88 Instruction Set**

| Mnemonic    | Description                  |                                                                         | us bits  |   |

|-------------|------------------------------|-------------------------------------------------------------------------|----------|---|

| ADDLW k     | Add literal and W            | w + k → destination                                                     | C,DC,Z   |   |

| ADDWF f, d  | Add W and f                  | w + f → destination                                                     | C,DC,Z   | 1 |

| ANDLW k, d  | AND literal and W            | w and k → destination                                                   | Z        | 1 |

| ANDWF f, d  | AND W and f                  | w and f → destination                                                   | Z        | 1 |

| BCF f, b    | Bit Clear f                  | 0 → f <b></b>                                                           |          | 1 |

| BSF f, b    | Bit Set f                    | 1 → f <b></b>                                                           |          | 1 |

| BTFSC f, b  | Bit Test f, Skip if Clear    | skip if f <b> = 0 <i>(2 Cycles)</i></b>                                 |          | 1 |

| BTFSS f, b  | Bit Test f, Skip if Set      | skip if f <b> = 1 <i>(2 Cycles)</i></b>                                 |          | 1 |

| CALL k      | Call Subroutine              | PC → TOS, k → PC[10:0]                                                  |          | 2 |

|             |                              | PCLATH[4:3] → PC[12:11]                                                 |          |   |

| CLRF f      | Clear f                      | 0x00 → f, 1 → Z                                                         | Z        | 1 |

| CLRW        | Clear W                      | 0×00 → w, 1 → Z                                                         | Z        | 1 |

| CLRWDT      | Clear Watchdog Timer         | 0×00 → WDT, 1 → TO, 1 → PD                                              | TO, PD   | 1 |

| COMF f, d   | Compliment f                 | f - 0xFF → destination                                                  | Z        | 1 |

| DECF f, d   | Decrement f                  | f - 1 → destination                                                     | Z        | 1 |

| DECFSZ f, d | Decrement f and Skip if Zero | f - 1 → destination                                                     |          | 1 |

|             |                              | skip if result = 0 <i>(2 Cycles)</i>                                    |          |   |

| GOTO k      | Go to address                | k → PC[10:0]                                                            |          | 2 |

|             |                              | PCLATH[4:3] → PC[12:11]                                                 |          |   |

| INCF f, d   | Increment f                  | F + 1 → destination                                                     | Z        | 1 |

| INCFSZ f, d | Increment f and Skip if Zero | F + 1 → destination                                                     |          | 1 |

|             |                              | skip if result = 0 <i>(2 Cycles)</i>                                    |          |   |

| IORLW k, d  | Inclusive OR literal with W  | w or k → destination                                                    | Z        | 1 |

| IORWF f, d  | Inclusive OR W with f        | w or f → destination                                                    | Z        | 1 |

| MOVF f, d   | Move f                       | f → destination                                                         | Z        | 1 |

| MOVLW k     | Move literal to W            | k → w                                                                   |          | 1 |

| M0VWF f     | Move W to f                  | w → f                                                                   |          | 1 |

| NOP         | No Operation                 | No Operation                                                            |          | 1 |

| RETFIE      | Return from interrupt        | TOS $\rightarrow$ PC, 1 $\rightarrow$ GIE                               |          | 2 |

| RETLW k     | Return with literal in W     | k → w, TOS → PC                                                         |          | 2 |

| RETURN      | Return from Subroutine       | TOS → PC                                                                |          | 2 |

| RLF f, d    | Rotate Left f through Carry  | C << f << C → destination                                               | С        | 1 |

| RRF f, d    | Rotate Right f through Carry | C >> f >> C → destination                                               | С        | 1 |

| SLEEP       | Enter Standby Mode           | $0 \times 00 \rightarrow WDT$ , $1 \rightarrow TO$ , $0 \rightarrow PD$ | TO, PD   | 1 |

| SUBLW k     | Subtract W from literal      | k - w → destination                                                     | C, DC, Z | 1 |

| SUBWF f, d  | Subtract W from f            | f - w → destination                                                     | C, DC, Z | 1 |

| SWAPF f, d  | Swap nibbles in f            | f[3:0] → destination [7:4]                                              |          | 1 |

|             |                              | $f[7:4] \rightarrow \text{destination} [3:0]$                           |          |   |

| XORLW k, d  | Exclusive OR literal with W  | w xor k → destination                                                   | Z        | 1 |

| XORWF f, d  | Exclusive OR W with f        | w xor f → destination                                                   | Z        | 1 |

k = 8 bit Literal or 11 bit Address, f = File Register, d = Destination (w or f) if omitted will default to f skip instructions add an extra cycle if condition is true (BTFSC, BTFSS, DECFZ, INCFZ)

| Mnemonic             | Description                                           | Operation Status                                                      | bits    |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------|---------|

| ADDCF f, d           | Add Carry to File Register                            | btfsc STATUS, C<br>incf f, d                                          | Z       |

| ADDDCF f, d          | Add Digit Carry to File Register                      | btfsc STATUS, DC<br>incf f, d                                         | Z       |

| BC k                 | Branch on Carry                                       | btfss STATUS, C<br>goto k                                             |         |

| BNC k                | Branch on Not Carry                                   | btfsc STATUS, C<br>goto k                                             |         |

| BDC k                | Branch on Digit Carry                                 | btfss STATUS, DC<br>goto k                                            |         |

| BNDC k               | Branch on Not Digit Carry                             | Btfsc STATUS, DC<br>goto k                                            |         |

| BZ k                 | Branch on Zero                                        | btfss STATUS, Z<br>goto k                                             |         |

| BNZ K                | Branch on Not Zero                                    | btfsc STATUS, Z<br>goto k                                             |         |

| CLRC<br>CLRDC        | Clear Carry<br>Clear Digit Carry                      | bcf STATUS, C<br>bcf STATUS, DC                                       | C<br>DC |

| CLRZ<br>LCALL K      | Clear Zero<br>Long Call                               | bcf STATUS, Z<br>bcf/bsf STATUS, RP0<br>bcf/bsf STATUS, RP1<br>call k | Z       |

| LGOTO k              | Long Goto                                             | bcf/bsf STATUS, RP0<br>bcf/bsf STATUS, RP1<br>goto k                  |         |

| MOVFW f<br>NEGF f, d | Move File Register to W<br>Negate File Register       | movf, 0<br>comf f, 1<br>incf f, d                                     | Z<br>Z  |

| SETC<br>SETDC        | Set Carry<br>Set Digit Carry                          | bsf STATUS, C<br>bsf STATUS, DC                                       | C<br>DC |

| SETZ<br>SKPC         | Set Zero<br>Skip on Carry                             | bsf STATUS, Z<br>btfss STATUS, C                                      | Z       |

| SKPNC<br>SKPDC       | Skip on Not Carry<br>Skip on Digit Carry              | btfsc STATUS, C<br>btfss STATUS, DC                                   |         |

| SKPNDC<br>SKPZ       | Skip on Not Digit Carry<br>Skip on Zero               | btfsc STATUS, DC<br>btfss STATUS, Z                                   |         |

| SKPNZ<br>SUBCF f, d  | Skip on Not Zero<br>Subtract Carry from File Register | btfsc STATUS, Z<br>btfsc STATUS, C<br>decf f, d                       | Z<br>Z  |

| SUBDCF f, d          | Subtract Digit Carry from File<br>Register            | btfsc STATUS, DC<br>decf f, d                                         | Z       |

| TSTF                 | Test File Register for Zero                           | movf f, 1                                                             | Z       |

# **MPASM Pseudo Instruction Set** (mini macros for the midrange PIC)

# Firefly 16F88 Special File Registers & RAM

The following tables are designed to supplement the 16F88 datasheet by Microchip.

|        | Green = bit set on POR "1" (Power On Reset)            |

|--------|--------------------------------------------------------|

|        | White = bit clear on POR "0"                           |

|        | Yellow = unknown on POR (not cleared or set)           |

|        | X = not in use, usually returns a zero "0"             |

| Italic | Italic = bit is read only                              |

|        | RAM unknown state on reset (not cleared or set on POR) |

|        | Red = Firefly Hardware does not support this feature   |

| Common to banks 0,1,2 & 3 (all banks)                         |          |                                                       |        |          |           |           |                       |      |

|---------------------------------------------------------------|----------|-------------------------------------------------------|--------|----------|-----------|-----------|-----------------------|------|

|                                                               | Bit 7    | 6                                                     | 5      | 4        | 3         | 2         | 1                     | 0    |

| FSR                                                           | Indirect | Indirect Data Memory(RAM or SFR) Address Pointer      |        |          |           |           |                       |      |

| INDF                                                          | Contents | Contents of Data Memory(RAM or SFR) Pointed to by FSR |        |          |           |           |                       |      |

| INTCON                                                        | GIE      | PEIE                                                  | TMRØIE | INTØIE   | RBIE      | TMRØIF    | INTØIF                | RBIF |

| PCL                                                           | Program  | Counter (                                             | (LSB)  |          | •         |           |                       |      |

| PCLATH                                                        | $\geq$   | $\geq$                                                | $\geq$ | Write Bu | iffer for | Upper fiv | e PCL bi <sup>.</sup> | ts   |

| STATUS                                                        | IRP      | RP1                                                   | RPØ    | NOT_TO   | NOT_PD    | Ζ         | DC                    | С    |

| RAM 0x070 - 0x07F                                             |          |                                                       | STATUS | XXXXXXXX |           | ·         |                       |      |

| Note: the ICD2 debugger mode uses DAM eddress 0x070 and 0x050 |          |                                                       |        |          |           |           |                       |      |

Note: the ICD2 debugger mode uses RAM address 0x070 and 0x0F0

#### Specific to bank 0 (PORTB & TMR0 repeated in bank 2)

|             | Bit 7                                    | 6                     | 5         | 4                       | 3                      | 2          | 1          | 0       |

|-------------|------------------------------------------|-----------------------|-----------|-------------------------|------------------------|------------|------------|---------|

| ADCONØ      | ADCS1                                    | ADCS0                 | CHS2      | CHS1                    | CHS0                   | GO         | $\searrow$ | ADON    |

| ADRESH      | A/D Resu                                 | <mark>lt Regis</mark> | ter (MSB) |                         |                        |            |            |         |

| CCP1CON     | $\ge$                                    | $\geq$                | CCP1X     | CCP1Y                   | CCP1M3                 | CCP1M2     | CCP1M1     | CCP1M0  |

| CCPR1H      | Capture/                                 | Compare/I             | PWM Regis | <mark>ter 1 (MS</mark>  | B)                     |            |            |         |

| CCPR1L      | Capture/                                 | /Compare/I            | PWM Regis | ter 1 (LS               | B)                     |            |            |         |

| PIR1        | $\left \right\rangle$                    | ADIF                  | RCIF      | TXIF                    | SSPIF                  | CCP1IF     | TMR2IF     | TMR1IF  |

| PIR2        | OSFIF                                    | CMIF                  | $\ge$     | EEIF                    | $\ge$                  |            | $\geq$     | $\ge$   |

| PORTA       | Bit 4 is Zero on BOR ->                  |                       |           |                         |                        |            | -          |         |

| PORTB       | <pre>&lt;- Bits</pre>                    |                       |           | 7 & 6 are Zeroed on BOR |                        |            |            |         |

| RCSTA       | SPEN                                     | RX9                   | SREN      | CREN                    | ADDEN                  | FERR       | 0ERR       | RX9D    |

| RCREG       |                                          |                       | ta Regist |                         |                        |            |            |         |

| SSPBUF      | Synchror                                 | nous Seria            | al Port R | eceive/Tr               | <mark>ansmit Bu</mark> | ffer       |            |         |

| SSPCON      | WCOL                                     | SSPOV                 | SSPEN     | СКР                     | SSPM3                  | SSPM2      | SSPM1      | SSPM0   |

| T1CON       | $\ge$                                    | T 1RUN                | T1CKPS1   | T1CKPS0                 | T10SCEN                | NOT_T1SYNC | TMR1CS     | TMR10N  |

| T2CON       | $\left \right\rangle$                    | TOUTPS3               |           | POUTPS1                 | TOUTPSØ                | TMR20N     | T2CKPS1    | T2CKPS0 |

| TMR0        | Timer0 Module Register                   |                       |           |                         |                        |            |            |         |

| TMR1H       |                                          |                       | for 16-b  |                         |                        |            |            |         |

| TMR1L       | Holding Register for 16-bit Timer1 (LSB) |                       |           |                         |                        |            |            |         |

| TMR2        | Timer2 Module Register                   |                       |           |                         |                        |            |            |         |

| TXREG       | USART Transmit Data Register             |                       |           |                         |                        |            |            |         |

| RAM 0x020 - | - 0x06F STATUS x00xxxxx                  |                       |           |                         |                        |            |            |         |

## Firefly 16F88 Special File Registers & RAM continued...

| Specific LU | Dank I (UPIION_REG & IRISD repeated in Dank 5) |                                                               |              |            |               |            |         |         |

|-------------|------------------------------------------------|---------------------------------------------------------------|--------------|------------|---------------|------------|---------|---------|

| -           | Bit 7                                          | 6                                                             | 5            | 4          | 3             | 2          | 1       | 0       |

| ADCON1      | ADFM                                           | ADCS2                                                         | VCFG1        | VCFGØ      | $\geq$        | $\geq$     | $\geq$  | $\geq$  |

| ADRESL      | A/D Resul                                      | t Regist.                                                     | er (LSB      | )          |               |            |         |         |

| ANSEL       | $\geq$                                         | ANS6                                                          | ANS5         | ANS4       | ANS3          | ANS2       | ANS1    | ANSØ    |

| CMCON       | C20UT                                          | C10UT                                                         | C2INV        | C1INV      | CIS           | CM2        | CM1     | CM0     |

| CVRCON      | CVREN                                          | CVROE                                                         | CVRR         | $\searrow$ | CVR3          | CVR2       | CVR1    | CVR0    |

| OSCCON      | $\searrow$                                     | IRCF2                                                         | IRCF1        | IRCF0      | OSTS          | IOFS       | SCS1    | SCSØ    |

| OPTION_REG  | NOT_RBPU                                       | INTEDG                                                        | TØCS         | TØSE       | PSA           | PS2        | PS1     | PS0     |

| OSCTUNE     | $\geq$                                         | $\sum$                                                        | TUN5         | TUN4       | TUN3          | TUN2       | TUN1    | TUN0    |

| PCON        | $\geq$                                         |                                                               | $\mathbf{i}$ | $\sim$     |               | $\geq$     | NOT_POR | NOT_BOR |

| PIE1        | $\geq$                                         | ADIE                                                          | RCIE         | TXIE       | SSPIE         | CCP1IE     | TMR2IE  | TMR1IE  |

| PIE2        | OSFIE                                          | CMIE                                                          | $\geq$       | EEIE       |               | $\geq$     | $\geq$  | $\geq$  |

| PR2         | Timer2 Pe                                      | riod Reg                                                      | ister        |            |               |            |         |         |

| TRISA       |                                                | /                                                             | PORTA, 5     | PORTA Da   | ata Direction | n Register | •       |         |

| TRISB       | PORTB Dat                                      | PORTB Data Direction Register (1 = input default), 0 = output |              |            |               |            |         |         |

| TXSTA       | CSRC                                           | TX9                                                           | TXEN         | SYNC       |               | BRGH       | TRMT    | TX9D    |

| SSPADD      | Synchrond                                      | ous Seria                                                     | l Port       | Address (I | 2C mode)      |            |         |         |

| SSPSTAT     | SMP                                            | CKE                                                           | D_A          | I2C_STOP   | I2C_START     | R_W        | UA      | BF      |

| RAM 0x0A0 - |                                                |                                                               | STATU        | S x01xxxxx |               |            |         |         |

Specific to bank 1 (OPTION\_REG & TRISB repeated in bank 3)

Specific to bank 2(PORTB & TMR0 repeated in bank 2)

|             | Bit 7                  | 6      | 5                                                                           | 4        | 3         | 2         | 1         | 0        |

|-------------|------------------------|--------|-----------------------------------------------------------------------------|----------|-----------|-----------|-----------|----------|

| EEADR       |                        |        |                                                                             |          | EEPRO     | M Address | s Registe | er (LSB) |

| EEADRH      | $\geq$                 | $\geq$ | $\geq$                                                                      | $\geq$   |           | M Address | _         |          |

| EEDATA      |                        |        |                                                                             |          | EE        | PROM Data | a Registe | er (LSB) |

| EEDATH      | $\geq$                 | $\geq$ |                                                                             |          | EE        | PROM Data | a Registe | er (MSB) |

| PORTB       |                        |        | <- Bits                                                                     | 7 & 6 ar | e Zeroed  | on BOR    |           |          |

| TMR0        | Timer0 Module Register |        |                                                                             |          |           |           |           |          |

| WDTCON      | $\geq$                 | $\geq$ | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | WDTPS3   | WDTPS2    | WDTPS1    | WDTPS0    | SWDTEN   |

| RAM 0x110 - | 0x16F                  |        |                                                                             | STATUS   | S x10xxxx | X         |           |          |

Specific to bank 3(OPTION\_REG & TRISB repeated in bank 1)

|             | Bit 7                         | 6                                                   | 5     | 4    | 3     | 2    | 1   | 0   |

|-------------|-------------------------------|-----------------------------------------------------|-------|------|-------|------|-----|-----|

| EECON1      | EEPGD                         | $\succ$                                             | $\ge$ | FREE | WRERR | WREN | WR  | RD  |

| EECON2      | EEPROM Con                    | EEPROM Control Register 2 (Not a physical register) |       |      |       |      |     |     |

| OPTION_REG  | NOT_RBPU                      | INTEDG                                              | TOCS  | TØSE | PSA   | PS2  | PS1 | PS0 |

| TRISB       | PORTB Data Direction Register |                                                     |       |      |       |      |     |     |

| RAM 0x190 - | STATUS x11xxxxx               |                                                     |       |      |       |      |     |     |

\*Keep in mind pins that support A/D will default to analog mode. To configure the pins as digital I/O on Fireflys 16F88 don't forget to clear the ANSEL register bits.

clrf ANSEL ;B1 will make all PORTA pins digital

#### The 16F88 configuration word

Configuration \_\_CONFIG bits setup the processor what to do when initially powered up. They are often referred to as fuses and a blank or erased PIC will set the config bits *fuses* and they are "blown" at programming time. They are in memory locations that cannot be accessed or modified by 16xxx series PICs, they can only be accessed / changed by a programmer such as Inchworm.

The list below shows only settings that apply to the Firefly Tutor, not listed are any config settings that would not apply to the Fireflys 16F88. When a PIC is erased the config bits return to their default set state.

#### Firefly mandatory config bit settings

To ensure your Firefly will operate properly the following three config options must be enabled. \_\_CONFIG \_CONFIG1, \_INTRC\_IO & \_DEBUG\_ON & \_LVP\_OFF

\_INTRC\_I0Internal RC oscillator enabled; RA6 & RA7 are available as I/O\_DEBUG\_0NDisable RB6 & RB7 as I/O; reserve for Inchworm use.\_LVP\_0FFFrees RB3 as I/O; Inchworm is a HVP programmer / Debugger

It's also possible to shorten the above statement to \_\_CONFIG \_CONFIG1, 0x377C

#### Additional options that depend on application

To add (actually AND) more config options simply use "&" to AND them together. \_\_CONFIG \_CONFIG1, 0x377C & \_CCP1\_RB3 It's also ok to use multiple CONFIG lines. \_\_CONFIG \_CONFIG1, \_WDT\_OFF & \_DEBUG\_ON \_\_CONFIG \_CONFIG1, \_CCP1\_RB0 & \_PWRTE\_ON

Default options are indicated with an asterisk.

| _CCP1_RB3 | CCP1 "PWM" (RB3/CON1 pin 3)                            |

|-----------|--------------------------------------------------------|

| _CCP1_RB0 | *default (IR_IN & SW1) handy for IR decoding "Capture" |

|           |                                                        |

| _WDT_ON   | *default Enables the Watchdog Timer                    |

| _WDT_OFF  | Disable Watchdog Timer (required for debug)            |

#### **Optional settings for CONFIG1**

| _CP_OFF           | *default code protect off                                                    |

|-------------------|------------------------------------------------------------------------------|

| _CP_ALL           | code protect on (PIC can only be erased and reprogrammed, read not possible) |

| _WRT_PROTECT_OFF  | *default no program memory is write protected                                |

| _WRT_PROTECT_256  | first <sup>1</sup> / <sub>4</sub> K program memory is write protected        |

| _WRT_PROTECT_2048 | first <sup>1</sup> / <sub>2</sub> program memory is write protected          |

| _WRT_PROTECT_ALL  | all program memory is write protected                                        |

| _CPD_ON           | EEPROM data is code protected                                                |

| _CPD_OFF          | *default EEPROM data code protect off                                        |

| _BODEN_ON         | *default brownout detect enabled                                             |

| _BODEN_OFF        | brownout detect disabled                                                     |

| _PWRTE_ON         | power on timer enabled (caution do not use when ICD2 debugging)              |

| _PWRTE_OFF        | *default power on timer disabled                                             |

Although the 16F88 has CONFIG2 fuse settings it is not used by Firefly and can be safely ignored.

Page 12 of 16 revised 9/4/2007

# All MPASM assembler programs should...

be [Tab] indented except for labels, comments

start with a processor directive

use the include file for that processor

finally end with the END directive

include "p16F88.inc"

END

## Compare and Jump if...

|                                           | X     | ( = RAM | X =   | LITERAL |

|-------------------------------------------|-------|---------|-------|---------|

| СЈА                                       | movf  | X, w    | movlw | Х       |

| Compare X to Y and jump if above          | subwf | Y, w    | subwf | Υ, w    |

| X > Y                                     | bnc   | ADDR    | bnc   | ADDR    |

| CJAE                                      | movf  | X, w    | movlw | Х       |

| Compare X to Y and jump if above or equal | subwf | Υ, ω    | subwf | Y, w    |

| $X \ge Y$                                 | bc    | ADDR    | bc    | ADDR    |

| СЈВ                                       | movf  | Υ, ω    | movlw | Х       |

| Compare X to Y and jump if below          | subwf | X, w    | subwf | Υ, w    |

| X < Y                                     | bnc   | ADDR    | bnc   | ADDR    |

| CJBE                                      | movf  | Υ, ω    | movf  | Y, w    |

| Compare X to Y and jump if below or equal | subwf | X, w    | sublw | Х       |

| X <= Y                                    | bc    | ADDR    | bc    | ADDR    |

| CJE                                       | movf  | X, w    | movlw | Х       |

| Compare X to Y and jump if equal          | xorwf | Υ, ω    | xorwf | Y, w    |

| X = Y                                     | bz    | ADDR    | bz    | ADDR    |

| CJNE                                      | movf  | X, w    | movlw | Х       |

| Compare X to Y and jump if not equal      | xorwf | Υ, ω    | xorwf | Y, w    |

| X <> Y                                    | bnz   | ADDR    | bnz   | ADDR    |

I've used the MPASM pseudo instruction "b" branch is used to simplify the above statements. Pseudo instructions will simply insert the code required at assembly time. In my opinion pseudo instructions can improve readability and shorted the apparent length of a program.

It's also possible to make any of the above functions into macros. For example: the **CJA** macro on the right.

|           | re and Jump if Above |

|-----------|----------------------|

| CJA macro | X, Y, ADDRESS        |

| movf      | Χ, w                 |

| subwf     | Y, W                 |

| bnc       | ADDRESS              |

| endm      |                      |

To use the **CJA** macro after it's declared simply use a statement similar to:

| CJA                     | cats, | dogs, | destination | ;       | i f  | cats    | $\rightarrow$ | dogs  | then | goto | destination   |          |

|-------------------------|-------|-------|-------------|---------|------|---------|---------------|-------|------|------|---------------|----------|

| 🗈 blueroomelectronics 🌞 |       |       |             |         |      |         |               |       |      | F    | Page 13 of 16 |          |

|                         |       |       | Sn          | art Kit | s bu | uild Sm | art           | Peopl | e    |      | revised       | 9/4/2007 |

# Firefly 16F88 Project:

"Blinky VR1"

This program will flash the three bicolor (Red/Green) LEDs in a back and forth fashion on your Firefly. You can adjust the speed with the potentiometer VR1.

|                |        | Ds 1 thru                                                                     | 3 will flash back and                             | (DIP switch VR1 = ON, Tutor = ON, all others OFF/down)<br>Forth with the rate controlled by VR1                                    |  |  |  |  |  |  |

|----------------|--------|-------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| _              |        |                                                                               | p=16F88<br><p16f88.inc></p16f88.inc>              | i                                                                                                                                  |  |  |  |  |  |  |

|                |        | ERRORLEV                                                                      | EL 0, -302<br>_CONFIG1, 0x2F30                    | ;<br>; suppress bank select warning                                                                                                |  |  |  |  |  |  |

|                | _let   | macro<br>movlw                                                                | reg, lit<br>lit                                   | ; MACRO _let <register>, <literal><br/>; W = literal</literal></register>                                                          |  |  |  |  |  |  |

|                |        | banksel<br>movwf<br>endm                                                      | reg<br>reg                                        | ; make sure it's in the right bank<br>; register = W                                                                               |  |  |  |  |  |  |

|                | Count  | equ<br>org                                                                    | 0x20<br>0x000                                     | ; delay loop counter (0x20 is RAM start location)<br>; this is the reset vector                                                    |  |  |  |  |  |  |

|                | Init   | nop<br>_let<br>_let                                                           | ANSEL, b'00000010'<br>ADCON0, b'11001101'         | ; nop if you plan on using the debugger<br>; select RA1/AN1 as analog input<br>; AD enabled, AN1 selected (VR1) & begin conversion |  |  |  |  |  |  |

| ,              | Red1   | _let                                                                          | PORTA, b'01000000'                                | ; LED1 RED                                                                                                                         |  |  |  |  |  |  |

| >              |        | _let<br>call                                                                  | TRISA, b'10111110'<br>Delay                       | ; R x x                                                                                                                            |  |  |  |  |  |  |

|                | Red2   | _let<br>_let                                                                  | PORTA, b'10000000'<br>TRISA, b'00111111'          | ; LED2 RED<br>; x R x                                                                                                              |  |  |  |  |  |  |

| >              | Red3   | call<br>_let<br>let                                                           | Delay<br>PORTA, b'00000001'<br>TRISA, b'01111110' | ; LED3 RED<br>; X X R                                                                                                              |  |  |  |  |  |  |

| >              |        | call                                                                          | Delay                                             | ,<br>,                                                                                                                             |  |  |  |  |  |  |

| >              | Green3 | _let<br>_let<br>call                                                          | PORTA, b'10000000'<br>TRISA, b'01111110'<br>Delay | ; LED3 GREEN<br>; x x G                                                                                                            |  |  |  |  |  |  |

|                | Green2 | _let<br>_let<br>call                                                          | PORTA, b'01000000'<br>TRISA, b'00111111'<br>Delay | ; LED2 GREEN<br>; x G x                                                                                                            |  |  |  |  |  |  |

|                | Green1 | _let<br>_let                                                                  | PORTA, b'00000001'<br>TRISA, b'10111110'          | ; LED1 GREEN<br>; G x x                                                                                                            |  |  |  |  |  |  |

| >              |        | call<br>goto                                                                  | Delay<br>Red1                                     | ; repeat forever                                                                                                                   |  |  |  |  |  |  |

|                | Delay  | ay ;*** Rotating VR1 varies loop delay, fast flashing LEDs will appear Orange |                                                   |                                                                                                                                    |  |  |  |  |  |  |

|                |        | bcf<br>movf<br>movwf                                                          | STATUS, RPØ<br>ADRESH, W<br>Count                 | ;B0 contains ADRESH, ADCON0 & Count<br>;B0 W = VR1 value 0x00-0xFF (also tests for zero)<br>;B0 let Count = W                      |  |  |  |  |  |  |

|                |        | bsf<br>bz                                                                     | ADCON0, GO<br>Exit                                | ;B0 start next conversion (Set A/D go/done bit)<br>; if Count = 0 then return early (no need to delay)                             |  |  |  |  |  |  |

| F              | Loop   |                                                                               | main delay loop begins                            |                                                                                                                                    |  |  |  |  |  |  |

|                |        | nop<br>decfsz                                                                 | Count                                             | ; stretches out the delay routine<br>;B0 Count = Count - 1, if result is zero then skip                                            |  |  |  |  |  |  |

| <del>ركر</del> |        | goto                                                                          | Loop                                              | ; not yet zero so loop                                                                                                             |  |  |  |  |  |  |

| \$             | Exit   | return                                                                        |                                                   | ; return                                                                                                                           |  |  |  |  |  |  |

|                |        | END                                                                           |                                                   |                                                                                                                                    |  |  |  |  |  |  |

#### **Firefly Templates**

The following templates are designed to aid in documenting your own firefly projects. It is simplified to show only available built in devices, external I/O ports & switch settings. You can use these templates for your own Firefly projects and documentation.

Both templates can be downloaded in PNG format and used with your Fireflys' project documentation from http://www.blueroomelectronics.com

Smart Kits build Smart People

blueroomelectronics

revised 9/4/2007

## Firefly and other f: blueroomelectronics + projects are available at

#### **Retail Sales**

CREATRON INC. 255 College St. Toronto Ontario, Canada Tel (416) 977-9258 Fax (416) 977-4700 creatronpart@hotmail.com http://www.creatroninc.com

#### **Online Sales**

#### dipmicro electronics

1251 Walkers Line, Burlington Ontario, Canada L7M4N8 Fax (866) 603-7109 http://www.dipmicro.com

#### **Dealer Sales & Technical Inquiries**

4544 Dufferin St. Toronto Ontario, Canada Tel (416) 897-1962 <u>sales@blueroomelectronics.com</u> <u>http://www.blueroomelectronics.com</u>

Info and all other inquiries info@blueroomelectronics.com

Page 16 of 16 revised 9/4/2007